如果说在过去五年左右的芯片设计中有一个突出的、全行业的趋势,那无疑就是小芯片(chiplet)的使用越来越多。随着芯片制造商希望它们能解决从芯片制造成本到设计的整体可扩展性等方方面面的问题,微型裸片已成为越来越普遍的特征。无论是简单地将以前的单片 CPU 拆分成几块,还是将47 个小芯片放在一个封装上,小芯片已经在今天的芯片设计中发挥着重要作用,芯片制造商已经明确表示它只是将来会成长。

与此同时,经过 5 年多的认真、大批量使用,小芯片和支撑它们的技术似乎终于在设计方面达到了一个拐点。芯片制造商已经对小芯片的好处(和坏处)有了更充分的了解,封装供应商已经改进了放置小芯片所需的超精确方法,工程团队已经解决了用于让小芯片相互通信的通信协议。

简而言之,小芯片不再是需要验证的实验性设计,而是已成为芯片制造商可以依赖的经过验证的设计。随着对小芯片技术的日益依赖,对设计路线图和稳定性的需求也随之而来——对设计标准的需求也顺势而至。

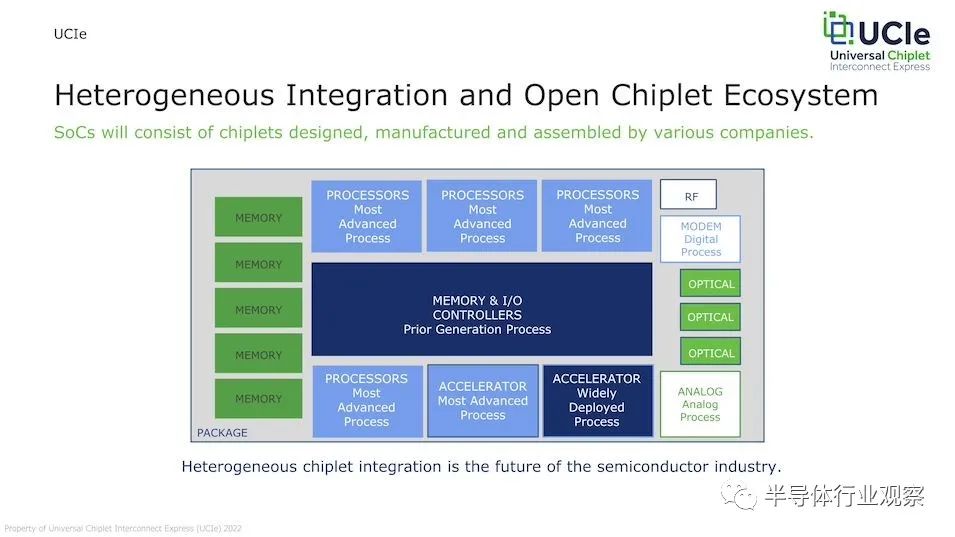

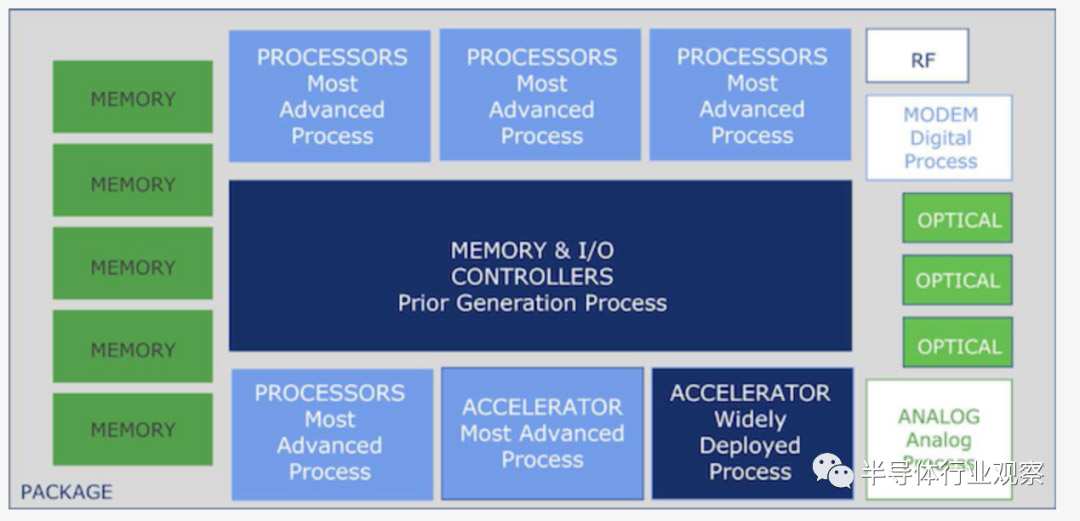

为此,今天英特尔、AMD、Arm 和所有三个领先的代工厂商齐聚一堂,宣布他们正在为小芯片互连制定一个新的开放标准,该标准被恰当地命名为UCIe(Universal Chiplet Interconnect Express,). 这个名字从非常成功的 PCI-Express 标准中汲取灵感,相关公司正在与 UCIe 一起创建连接小芯片的标准,目标是制定一套标准,不仅简化所有相关参与者的流程,而且引领走向来自不同制造商的小芯片之间的完全互操作性,允许芯片在芯片制造商认为合适的情况下混合和匹配小芯片。

换句话说,要从小芯片中构建一个完整且兼容的生态系统,就像今天的基于 PCIe 的扩展卡的生态系统一样。

与 PCIe 的比较适用于多个层面,这可能是快速了解 UCIe 小组目标的最佳方式。不仅新标准以开放的方式提供,相关公司还将在今年晚些时候建立一个正式的联盟组来管理 UCIe 并进一步开发它。同时,从一般技术的角度来看,小芯片的使用是集成电路不断整合的最新举措,因为越来越小的晶体管允许越来越多的功能被集成到芯片上。从本质上讲,到目前为止,一直在扩展卡或单独芯片上的功能正在开始进入芯片/SoC 本身。所以就像 PCIe 调节这些部件如何作为扩展卡一起工作一样,

最终,UCIe 背后的团队的既定目标是为小芯片建立一个开放且无处不在的生态系统。无论这意味着简单地将某些物理方面标准化以简化制造,还是实现真正的混合匹配设置,客户可以从多个芯片(let)制造商处请求使用小芯片构建的芯片,这些都需要一个强大的基础标准来实现。芯片制造行业的主要参与者都在支持 UCIe 以实现这一目标。

为什么是小芯片?

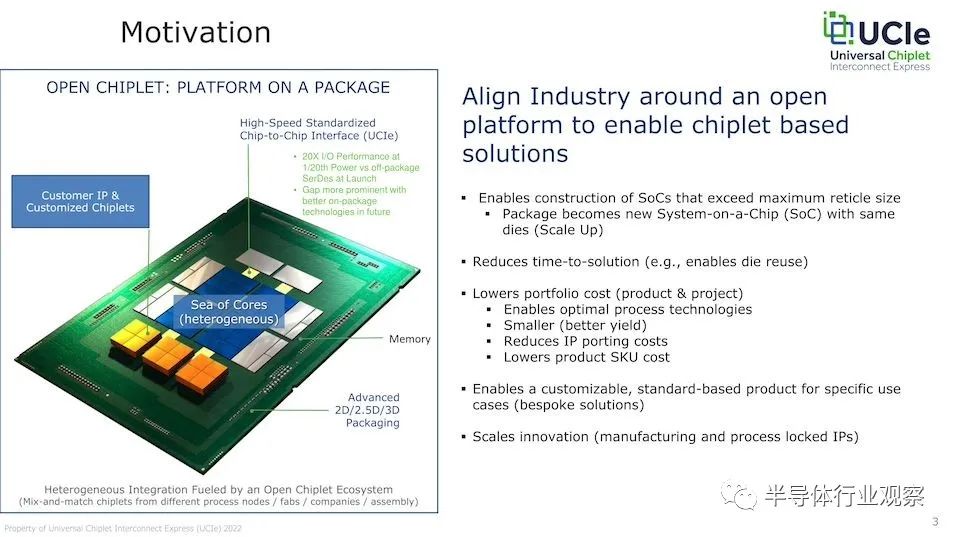

反过来,发生所有这一切的原因是Chiplet被越来越多地使用——在某些情况下更是唯一选择。小芯片已经被用于混合来自多个芯片制造商或来自多个工艺节点的裸片,并且它们被用于构建由于标线限制而无法实现的大型芯片。所有这些都是由某种方式的经济驱动(如不是为芯片的每个部分使用昂贵的尖端节点),或者是希望以一种比花费数年时间流片单片芯片更方便的方式结合不同制造商的 IP。可以肯定的是,单片芯片作为一个整体并没有完全消失(移动数据仍然很昂贵),但芯片设计的经济性正在无情地推动芯片在更多情况下的使用。

与此同时,对性能和效率的推动也推动了对小芯片的持续兴趣。或者更具体地说,推动了将更多功能集成到单个芯片封装上的愿望。PCIe 尽管速度很快,但按照芯片标准来看仍然很慢;从 CPU 到控制器(然后再返回)的长走线长度会增加很多延迟,并且将数据推送到那么远的地方在功率方面相对昂贵。因此,芯片制造商越来越希望将这些功能集成到芯片上,以降低延迟并降低功耗。对于小芯片(以及 UCIe),这意味着能够将性能提高 20 倍以上,并将功耗降低大致相同的数量。

UCIe 1.0:新的 Die-To-Die 规范,顶部有 PCIe 和 CXL,今日上市

深入研究 UCIe 规范的第一个修订版,我们发现一些非常简单的东西,以及围绕当今封装技术的功能非常明确地设计的东西。今天,UCIe 带来的不是新技术,而是当前技术的不同实现之间的标准化,以便每个人都有共同的基础来工作。

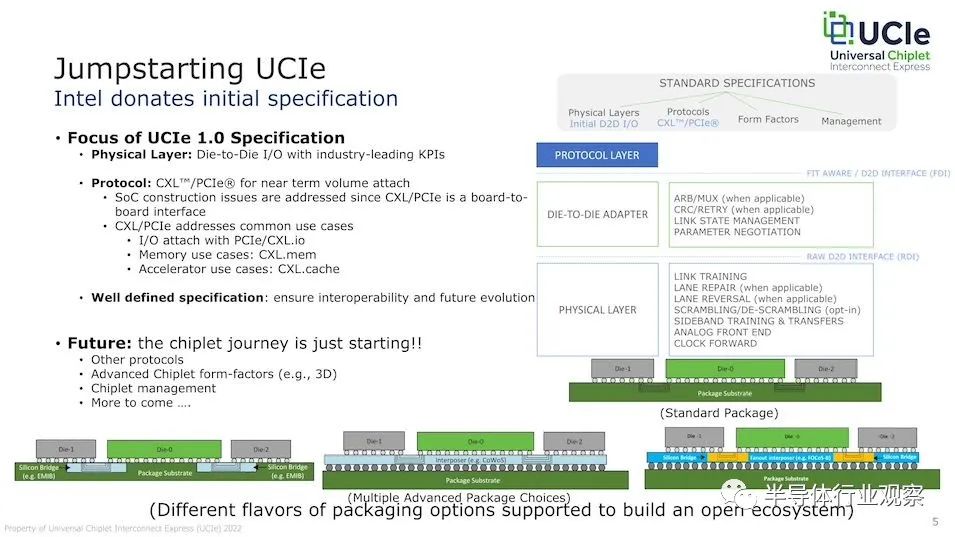

不足为奇的是,这个初始版本的 UCIe 来自英特尔,英特尔将规范贡献给业界,并将成为 UCIe 联盟。几十年来,英特尔一直负责多项备受瞩目的开放式互连技术的初步开发——其中最重要的是 USB、PCIe 和 Thunderbolt 3。但即使如此,在他们看中的下一波计算浪潮技术的基础上,看到他们捐赠零差距互连技术来帮助行业发展依然会让人有少许震惊。不过,请不要误会,这不是英特尔独有的举措,支持新标准的公司以及即将组建的联盟就是明证。(只要你看到有来自英特尔和 AMD 的高级研究员在同一个简报电话中,你就知道发生了大事)

UCIe 借鉴了英特尔早期的高级接口总线 (AIB) 技术。英特尔此前曾在 2020 年将该技术捐赠给 CHIPS 联盟,因此这不是英特尔第一次以开放的方式发布该技术的一个版本。但 UCIe 是迄今为止规模最大(也是最专注于小芯片)的努力,英特尔的晶圆厂竞争对手以及 CPU 设计竞争对手的支持就是明证。

至于UCIe规范本身,我们来谈谈它做了什么,不包括什么。该规范涵盖了物理层,列出了小芯片相互通信的电气信号标准,以及物理通道的数量和支持的凸块间距。该规范涵盖了协议层,定义了覆盖在这些信号上的更高级别的协议,以了解所有内容并提供必要的功能集。

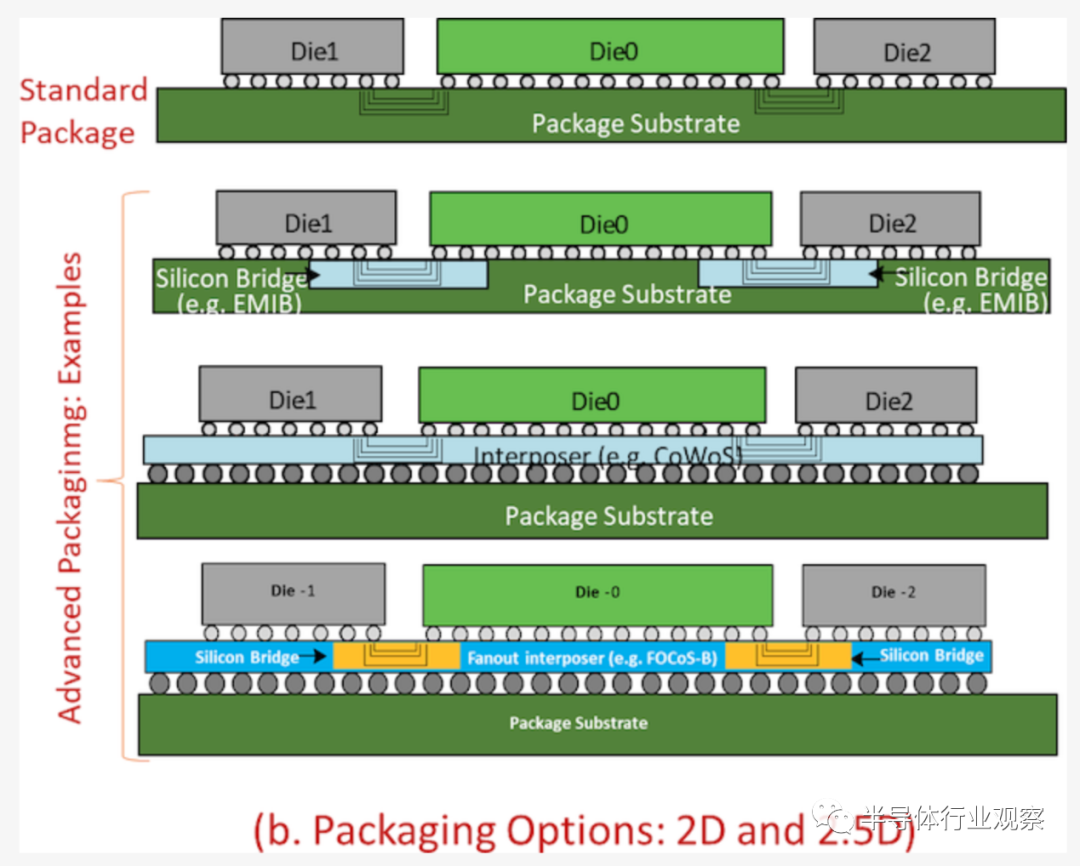

然而,规范没有涵盖的是用于在小芯片之间提供物理链接的封装/桥接技术。例如,这不是英特尔放弃 EMIB 或 Foveros。相反,UCIe 与桥接无关。小芯片可以通过扇出桥、硅中介层、EMIB 连接,甚至在带宽较低的设备的情况下,甚至只是一个普通的旧有机基板。UCIe 旨在与所有这些一起工作,因为桥本身本质上是一个dumb pipe ,用于在小芯片之间传输电信号。只要一个小芯片符合标准(包括凸块间距),它就可以与另一个 UCIe 小芯片通信。

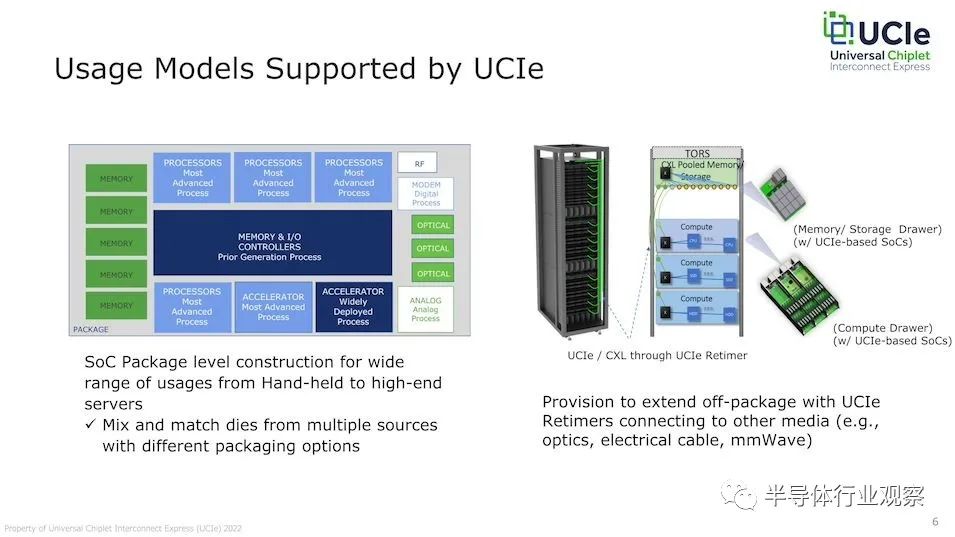

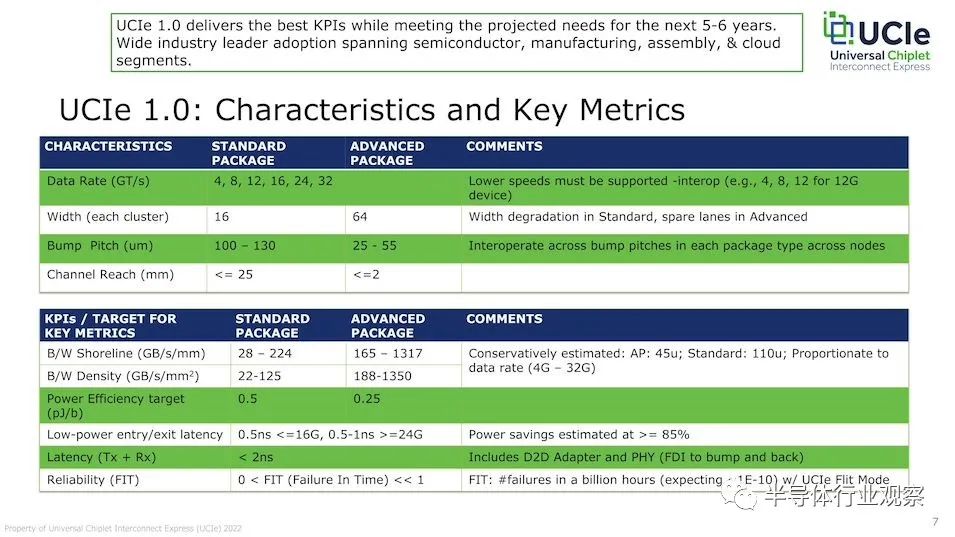

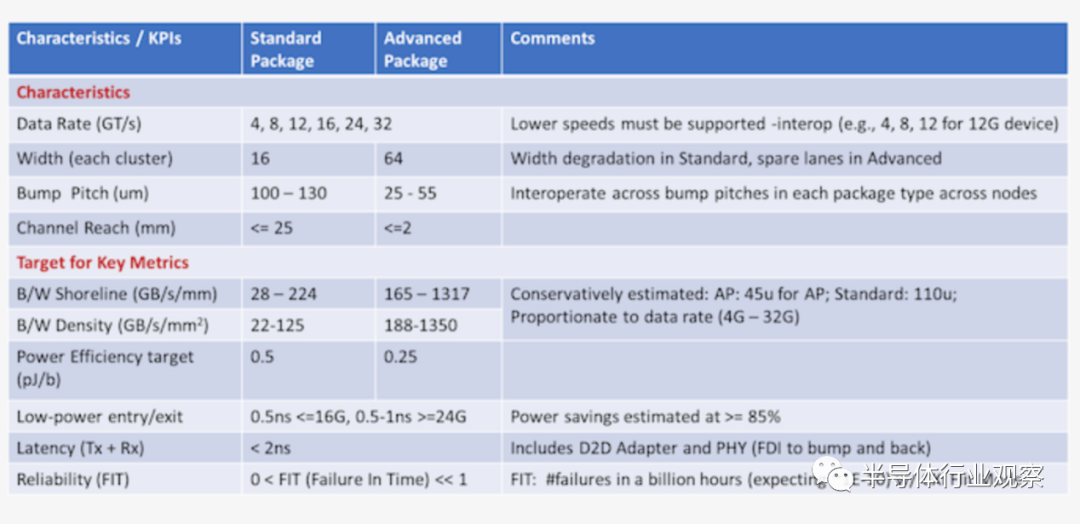

关于这一点,UCIe 1.0 基本上具有两个性能/复杂性标准级别。恰当命名的“标准封装”级别的规格是为使用传统有机基板的低带宽设备设计的。这些部件将使用多达 16 条数据通道、100μm + 凸块间距和扩展通道长度。在高层次上,这就像通过现代 PCIe 链路连接两个设备,但将它们放置得更近了。

同时,第二套规范涵盖了 UCIe 小组看似“高级封装”的内容,涵盖了所有基于高密度硅桥的技术,如 EMIB 和 InFO。先进的封装规格要求更小的凸块间距(大约 25μm 到 55μm)以及由于更高的密度和小于 2mm 的非常短的通道范围,每个集群的通道数是 4 倍。UCIe 推广者采用最全面的配置,相信采用当今 45μm 凸点间距技术的先进封装设置将能够提供高达 1.3TB/s/mm 的“ shoreline”(线性)带宽。也就是说,每秒1.3TB的数据可以从芯片的1mm边缘通过。

我不会在这里对每一个数字都详细解读,但可以肯定的是,所有这些都是为了强调 UCIe 是如何设置为满足性能范围两端的小芯片需求的。对于只需要以具有成本效益的方式将两个小芯片组合在一个封装上的芯片制造商来说,有标准封装方法。对于需要使两个小芯片的性能尽可能接近单个单片芯片的芯片制造商来说,先进的封装规范允许大量通道,从而提供大量带宽。

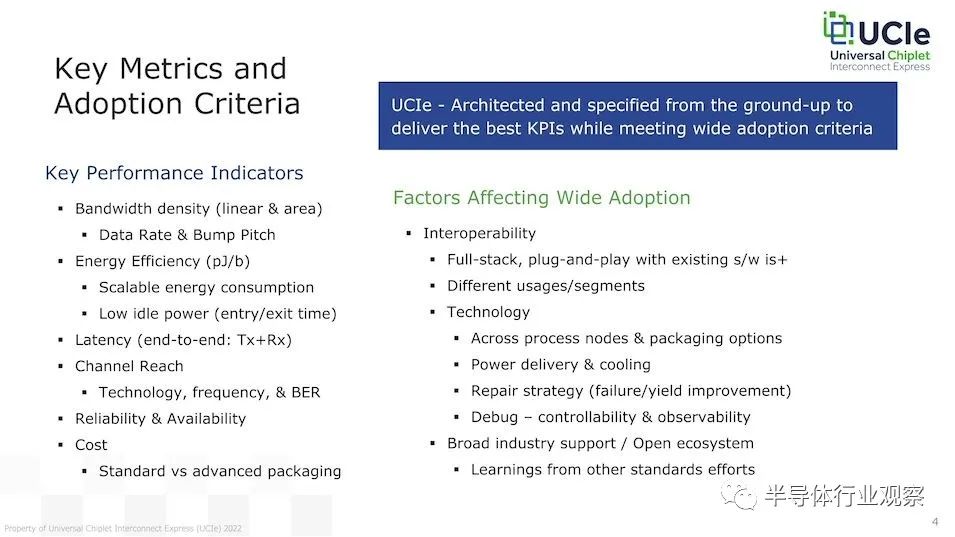

同时,有趣的是要注意发起人在延迟和能源效率方面的期望。对于所有封装类型,延迟预计将低于 2ns,这在拆分以前单片芯片设计的小芯片设计中尤其重要。同时,电源效率范围从标准封装的低 0.5 pJ/bit 到高级封装的更低 0.25 pJ/b。这有助于说明为什么一些芯片制造商渴望加入小芯片,因为对离散 PCIe/CXL 卡的改进可能是显着的。

反过来,连接小芯片的物理层对于 UCIe 来说是新的。英特尔和其他推动者并没有深入探讨其工作原理,但在较高级别上,物理层标准提供了电信号、时钟、链路训练和边带信号。一个 256 字节的流控制单元 (FLIT) 依次处理实际的数据传输。

在此之上是一个中间层,该组织称之为 Die-to-Die Adapter。D2D 为小芯片之间的链路状态管理和参数协商提供了基础。D2D 还负责通过 CRC 和链路级重试为额外的数据可靠性保护提供可选支持。

最后,在协议层,小芯片制造商有几个不同的选择。UCIe 的官方标准化协议是 PCI-Express 及其缓存一致的“表亲”,Compute Express Link,它本身构建在 PCIe 之上。在这里讨论他们的选择时,UCIe 的推动者选择了务实的方法:PCIe 和 CXL 已经得到了全行业的支持,因此他们不会自己重新发明轮子,而是要利用协议层的现有生态系统。这意味着 UCIe 正在以一个完全充实且经过充分验证的协议层开始运行,该协议层可以提供可靠的数据传输和链路管理,以及缓存一致性等额外的定制功能。也许同样重要的是,这意味着客户和芯片制造商都可以利用他们现有的 PCIe/CXL 软件投资,

在实践中,如果 UCIe没有以这种方式利用 PCIe/CXL ,我会感到更加惊讶。PCIe 技术已成为其他各种技术的支柱,整个行业已经不再试图在基本设备互连需求方面超越 PCIe。

也就是说,发起人已经明确表示,UCIe 并不仅限于 PCIe/CXL。如果出现某些问题并且所有者愿意将其捐赠给该标准,则该标准的未来版本可能会添加其他协议。

最后,芯片制造商也可以自由使用他们自己的定制/定制协议;它们不仅限于使用PCIe /CXL。UCIe 支持允许使用任何其他协议的原始/流式协议选项。当然,两个小芯片都需要支持这种自定义协议才能建立连接,但即使在这种情况下,这也将允许芯片制造商利用 UCIe 标准的物理方面来简化他们自己的设计/生产。

这也意味着现有的互连协议,例如 AMD 的 Infinity Fabric,即使引入了 UCIe,也不太可能出现在任何地方。像 IF 这样的协议仍然比 PCIe/CXL 的能力要复杂和专业得多,考虑到连接 CPU 内核和 I/O 芯片的非常具体的一致性要求,这是有道理的。换句话说,chiplet 设计的最前沿仍然领先于 UCIe 1.0 的起点。

长期发展:UCIe 也适用于外部互连?!

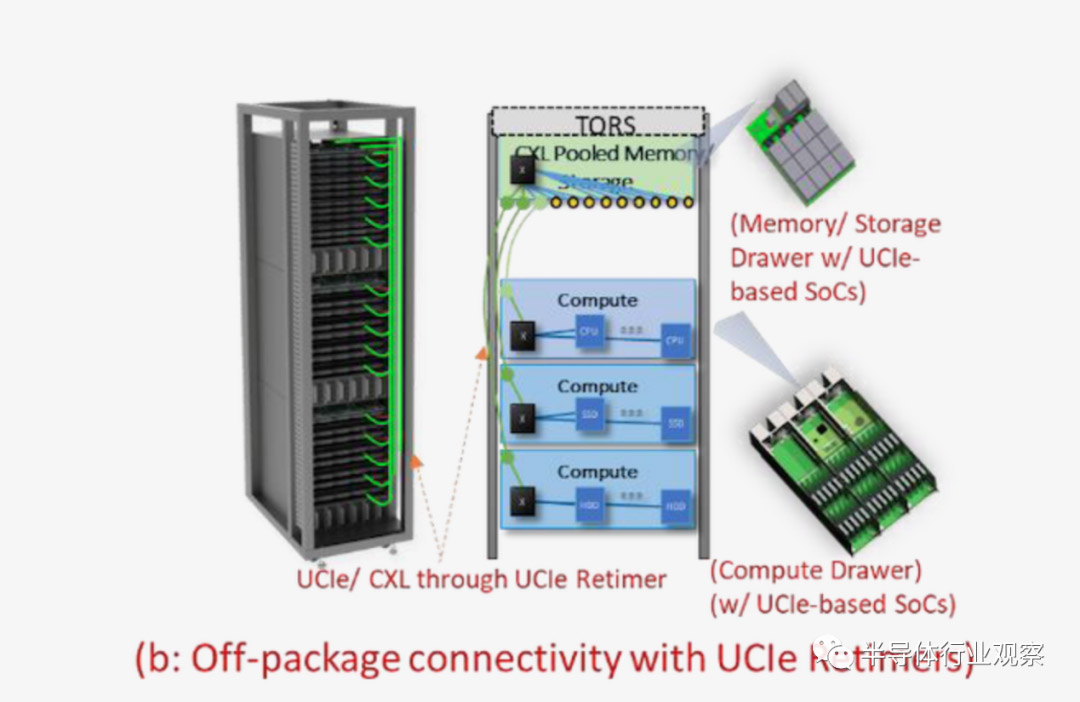

尽管 UCIe 的首要重点是为小芯片提供片上互连,但该标准实际上包含了片外的规定。芯片外的方式。

如果芯片/系统制造商愿意,该规范允许使用重定时器在协议级别传输更远距离的 UCIe。诚然,这确实通过增加(很多)距离而牺牲了延迟和功率优势。但是 UCIe 推广者设想服务器客户使用它在机架或 pod 级别提供 UCIe 连接,即使在长距离上也能提供直接的小芯片到小芯片的连接。

这种设置最有趣和最明显的用例是硅光子学。在那里扩展小芯片概念,芯片制造商可以在封装边缘构建一个共同封装的光收发器,然后使用 UCIe 将其连接到另一个小芯片。这将允许直接从芯片进行光学互连,绕过使用片外收发器的需求(和电力成本)。

发起人还展示了基于外部存储器/存储设备的概念。以及带有更多 SoC 的外部机架/绘图。

UCIe 1.0 只是一个开始

虽然今天发布了 UCIe 1.0 规范,但该标准的推动者已经将目光投向了该技术以及联盟本身的未来。

UCIe 1.0 在很大程度上是一个“起点”标准,它最初是在英特尔内部以单独的方式开发的。如前所述,该联盟将研究其他可能的协议添加到标准中。到目前为止,该标准只定义了他们认为是小芯片设计的四个方面中的两个:物理层和通信协议。该小组希望通过定义标准化的小芯片形状因素,甚至管理其他小芯片,进一步使混合搭配的小芯片生态系统成为现实。

这是在芯片封装技术不断变化的基础上,这些技术仍在进步。UCIe 1.0 标准基本上只针对 2D 和 2.5D 芯片封装定义,而不是像即将推出的 Foveros Direct 这样的 3D 直接芯片对芯片技术。随着 3D 芯片封装的推出,标准将需要更新以考虑提供的新功能以及更高的密度。

但为此,UCIe 将需要一个合适的联盟来支持它,这就是为什么今天的公告既是对新标准的启示,也是对其他公司加入并帮助开发标准的未来迭代的宣传。UCIe 发起人团体已经是一个非常庞大的名单,其中包括芯片/IP 设计师 AMD、Arm、英特尔和高通、芯片工厂台积电和三星(和英特尔)、芯片封装公司 Advanced Semiconductor Engineering 和云计算提供商谷歌、微软和 Meta的支持。